# Rechnersysteme

# Speicherorganisation und Adressierungsarten

# Otto-von-Guericke-Universität Magdeburg

### **Speicherorganisation**

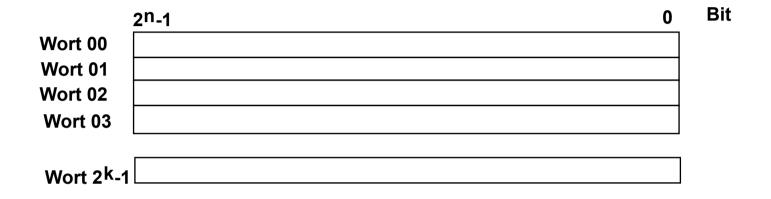

Wort-orientierter Speicher

Byte-orientierter Speicher

Vorteil: Kompakteres Abspeichern verschieden langer Befehle und Operanden

|                        | 7 | 0 | Bit |

|------------------------|---|---|-----|

| Byte 00                |   |   |     |

| Byte 01                |   |   |     |

| Byte 02                |   |   |     |

| Byte 03                |   |   |     |

| •                      |   |   |     |

| Byte 2 <sup>k</sup> -1 |   |   |     |

### **Speicherorganisation**

**Wort-orientierter Speicher**

3 - 0 Wort 00 7 - 4 Wort 01 B- 8 Wort 02

B- 8 Wort 02 F -C Wort 03

| ◀      |       | — (Lang-)V | Vort |        |      |     |        |   |                     |

|--------|-------|------------|------|--------|------|-----|--------|---|---------------------|

| 4      |       |            |      | (Ha    | ılb- | ) W | ort    |   |                     |

| 31 2   | 24 23 | 16         | 15   |        | 8    | 7   |        | 0 | Bit                 |

| Byte 0 |       | Byte 1     |      | Byte 2 |      |     | Byte 3 |   | A Donnolword        |

| Byte 0 |       | Byte 1     |      | Byte 2 |      |     | Byte 3 |   | <b>▼</b> Doppelword |

| Byte 0 |       | Byte 1     |      | Byte 2 |      |     | Byte 3 |   | •                   |

| Byte 0 |       | Byte 1     |      | Byte 2 |      |     | Byte 3 |   |                     |

|        | -     |            |      |        |      |     |        |   |                     |

| Wort 2 <sup>k</sup> -1 | Byte 0 | Byte 1 | Byte 2 | Byte 3 |

|------------------------|--------|--------|--------|--------|

| ****                   |        |        |        |        |

Quad-

Wort

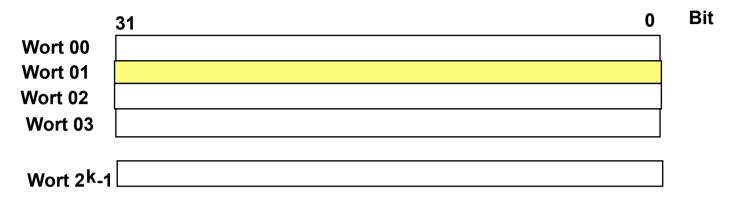

### **Big-Endian-Darstellung**

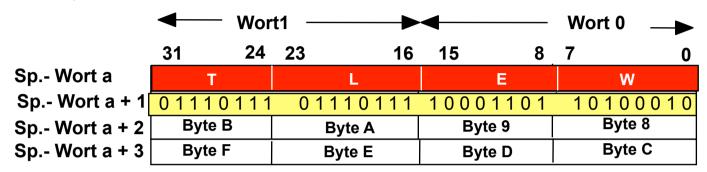

Beisp. Motorola 680x, H-Wort 1 H-Wort 0 68x00, SPARC, PowerPC 24 23 31 15 7 16 8 0 W Sp.- Wort a E 10100010 00001 **Sp.- Wort a + 1** Byte B Byte 8 Byte A Byte 9 **Sp.- Wort a + 2** Byte C Byte F Byte D Byte E **Sp.- Wort a + 3**

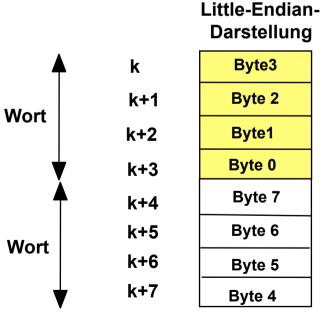

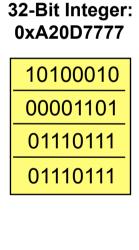

### Little-Endian-Darstellung

#### Beisp. Intel 80x86, ARM

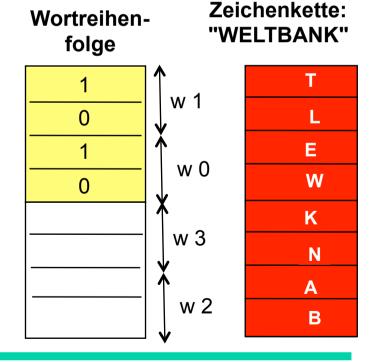

# Little-/Big-Endian-Darstellung

Zeichenkette: HELLO\_World

# Big - Endian

| BYTE-NR | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|

|         | Н | Е | L | Г | 0 | _ | W | 0 | R | L | D | ! |

### Little - Endian

| BYTE-NR | 3 | 2 | 1 | 0 | 3 | 2 | 1 | 0 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|

|         | L | Г | Е | I | 0 | W |   | 0 | ! | D | L | R |

Für 16-Bit Datentypendes MC 6809 wird die Big-Endian Darstellung verwendet

### 6809 Befehlsformate:

7 0

OPCODE

OPCODE Postbyte

OPCODE

1. Postbyte

2. Postbyte

OPCODE

1. Postbyte

2. Postbyte

3. Postbyte

OPCODE

OPCODE Erw.

1. Postbyte

2. Postbyte

3. Postbyte

1-Byte -Befehle - der Operand, falls vorhanden wird implizit durch den OPCODE bestimmt z.B. INCA

<sup>2</sup> -Byte -Befehle - Bedeutung des Postbytes: 1. kurze Adresse

2. nähere Bestimmung der Adressierung mit Index

3-Byte -Befehle - Bedeutung der Postbytes: 1. lange Adresse

2. nähere Bestimmung der Adressierung mit Index

OPCODE

OPCODE Erw.

1. Postbyte

2. Postbyte

4-Byte -Befehle ohne OPCODE Erw.

Bedeutung der Postbytes: nähere Bestimmung der

Adressierung mit Index

4-Byte -Befehle mit OPCODE Erw. Bedeutung der Postbytes: lange Adresse

5 -Byte -Befehle

oder

Bedeutung der Postbytes: nähere Bestimmung der Adressierung mit Index

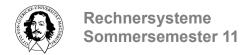

### Ziele beim Entwurf eines Adressierungsmechanismus

- großer Adreßraum

- kleines Adreßfeld in der Instruktion

- Komfort für den Programmierer

- positionsunabhängiger (verschieblicher) Code

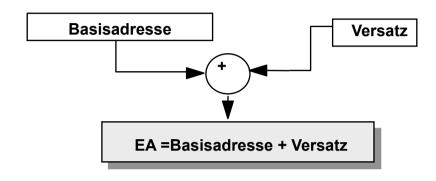

Lösung des Zielkonflikts zwischen Größe des AR und Größe des AF: Berücksichtigung von Lokalität der Berechnungen

Vereinfachung der Adressierung einfacher Datenstrukturen (Listen, Arrays)

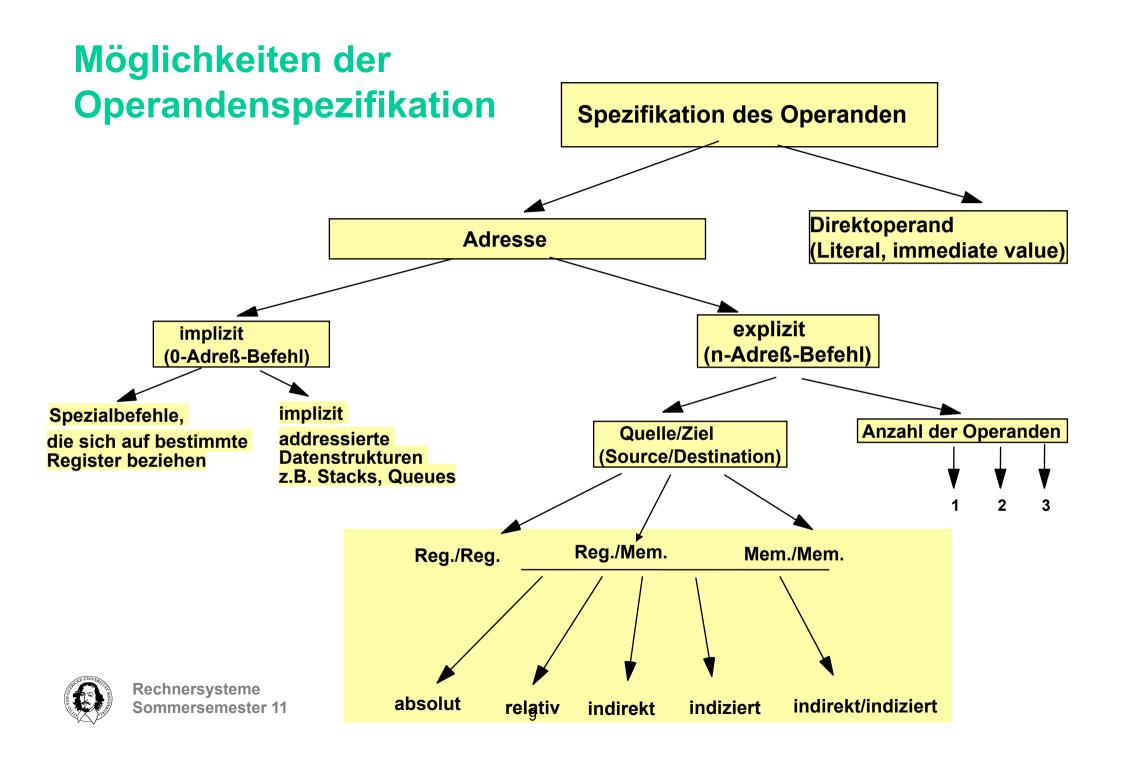

# **6809 Register Adressierung**

Befehle: TFR, EXG,

#### **Speicherplatz**

| OPCODE     |

|------------|

| Reg. Spec. |

|            |

|            |

|            |

|            |

S: Source

**D: Destination**

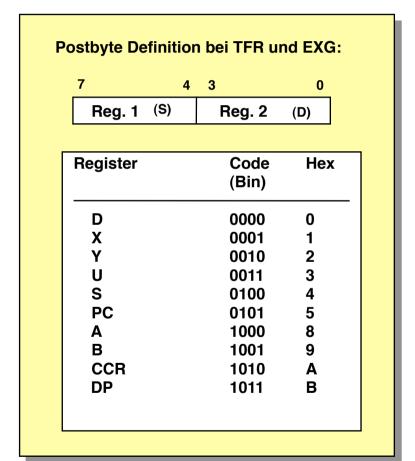

### Stack (Stapel, Keller, LIFO-Queue)

#### **PUSH:**

SP=MAX: Exception 'full'

SP← SP-1

Mem[SP] ← Register

SP >AMAX: Signal 'almost full'

**PULS:**

SP=BOS: Exception 'empty'

Register← Mem[SP]

SP<sup>←</sup> SP+1

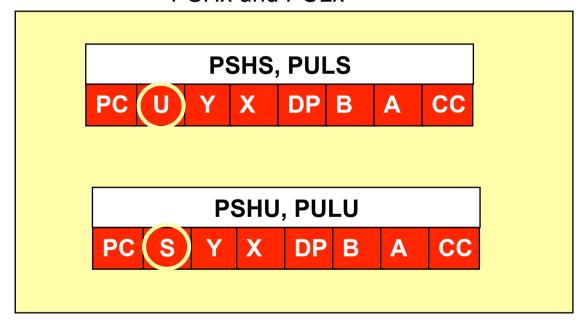

### 6809 Stack Adressierung

Befehle: PSHU, PSHS, PULU, PULS

#### **Speicherplatz**

m OPCODE

m+1 Register List.

m+2

m+3

m+4

Post-Byte Definition bei PSHx und PULx

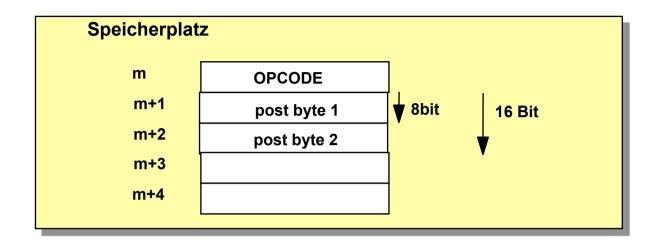

### 6809 Direktoperanden (unmittelbare Adressierung, engl.: immediate)

Beisp.: ADDA #\$95

m 8B m+1 95

PC = PC+2

ADDD #\$1295

m <u>C3</u> m+1 12 m+2 95

PC = PC+3

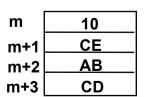

LDS #\$ABCD

PC = PC+4

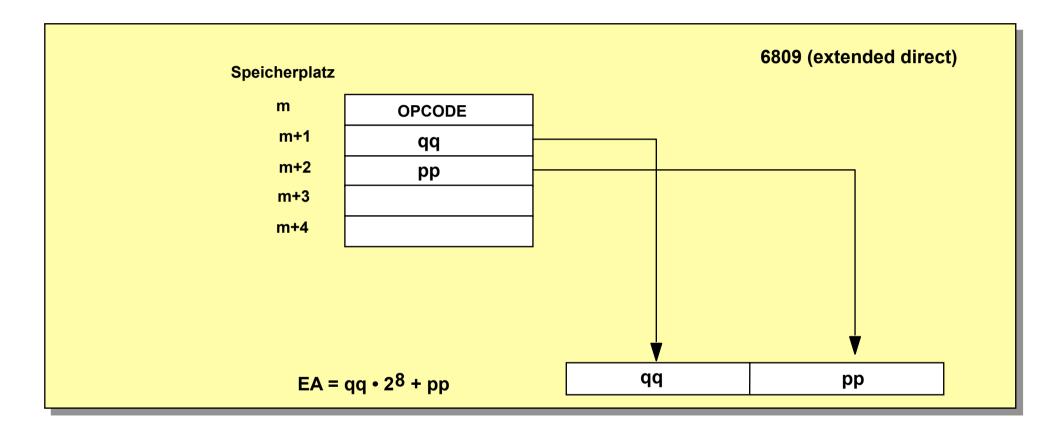

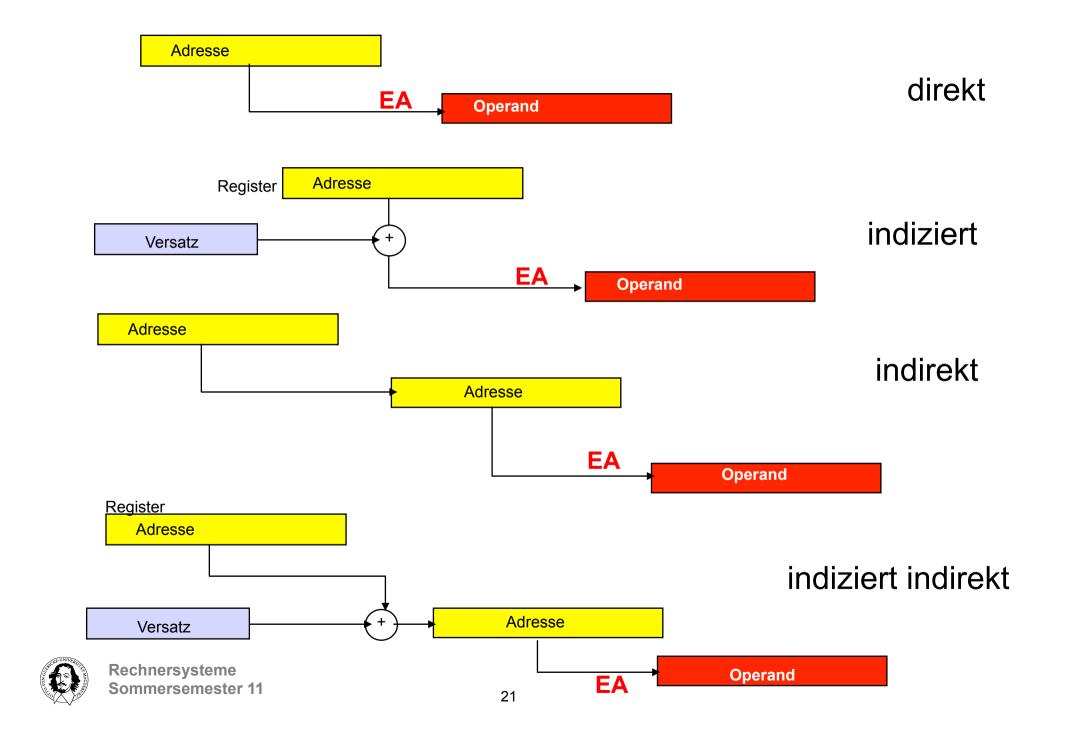

# Absolute (Direkte) Adressierung

Die effektive Adresse EA wird durch Konkatenation der beiden Post Bytes nach dem OPCODE gebildet. Das erste Post Byte (qq) gibt das höherwertige Byte, das zweite Postbyte (pp) das niederwertige Byte der EA an.

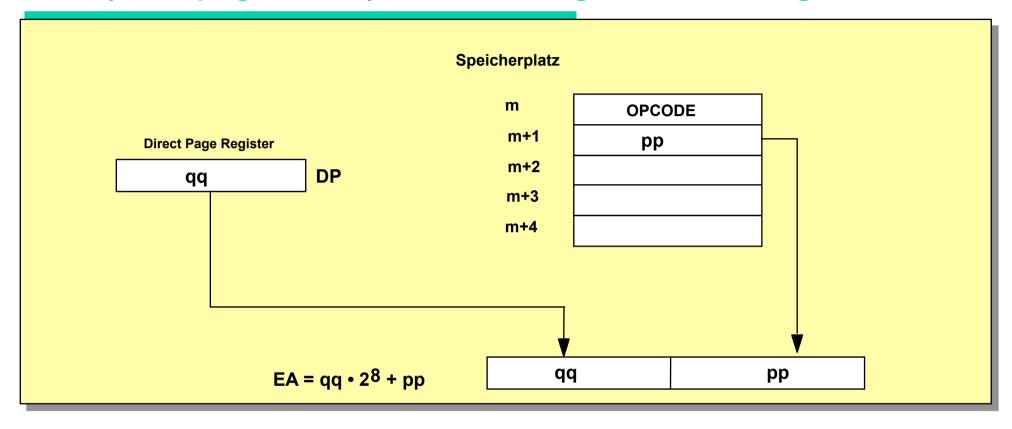

### 6809 (base page direct) Adressierung über Basisregister

Die effektive Adresse EA wird durch Konkatenation einer kurzen Adresse nach dem OPCODE mit dem Inhalt des Direct Page Registers (DP) gebildet. Die kurze Adresse gibt das niederwertige Byte, der Inhalt des DP das höherwertige Byte der EA an.

Das DP kann dynamisch durch einen Transferbefehle z.B. TFR A, DP geladen werden oder durch eine Assemblerdirective SETDP gesetzt werden.

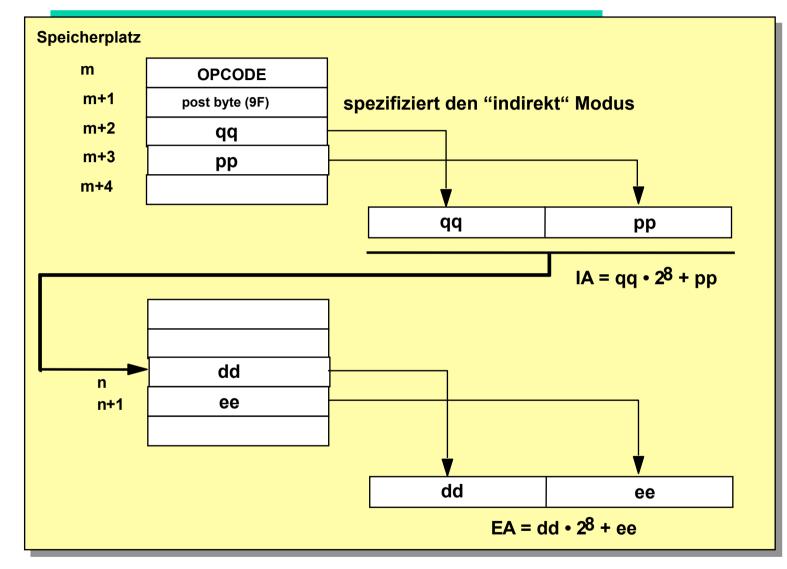

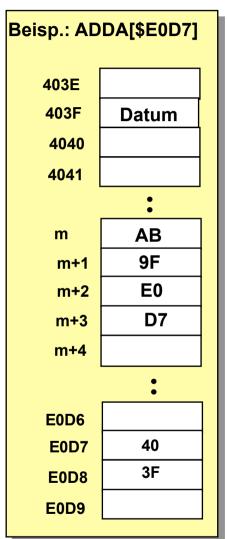

### 6809 (extended indirect) Indirekte Adressierung

Die dem OPCODE folgende Adresse gibt nicht an, wo sich die Daten für den Befehl befinden, sondern die Adresse, die auf die Daten zeigt (Unterstützung von Zeigern).

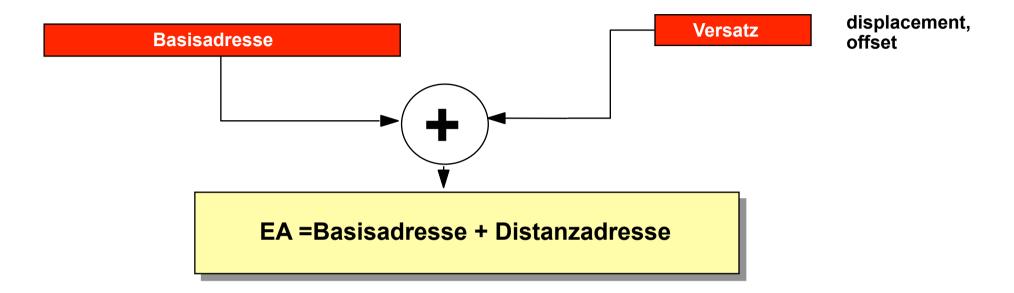

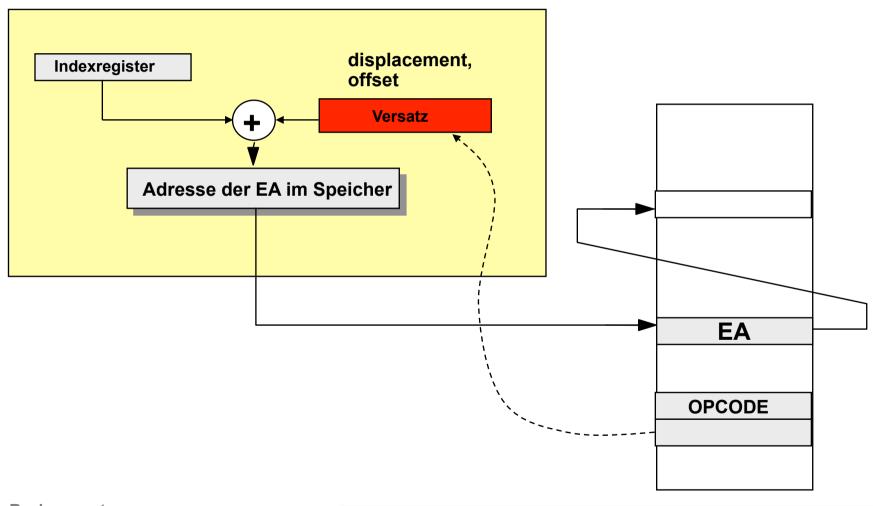

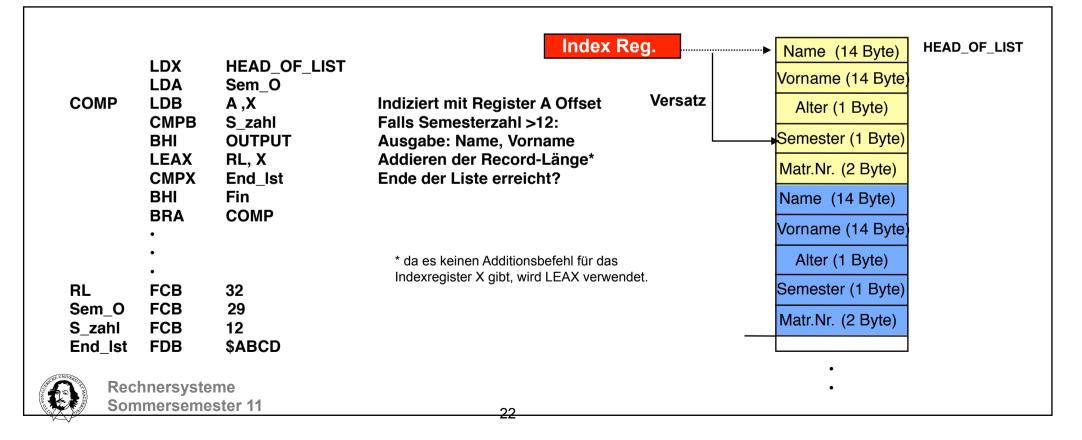

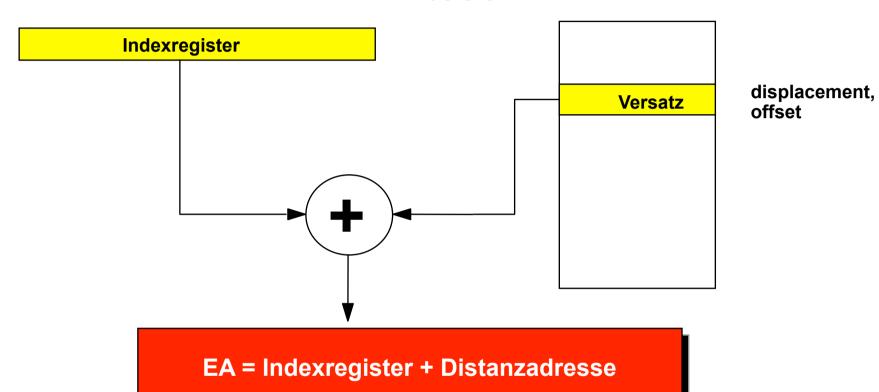

### Indizierte Adressierung (Indexed Adressing)

#### Wo steht die Basisadresse?

- Register: Indexregister

- Speicher: indirekte Adressierung

#### Wo steht der Versatz?

- Speicher (Literal)

- Register

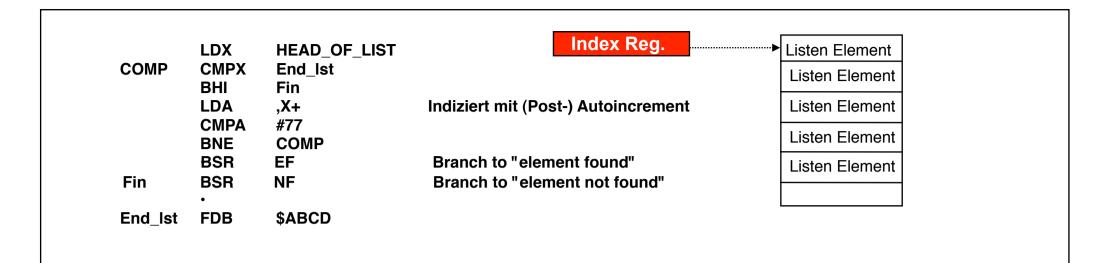

- Autoincrement /Autodecrement

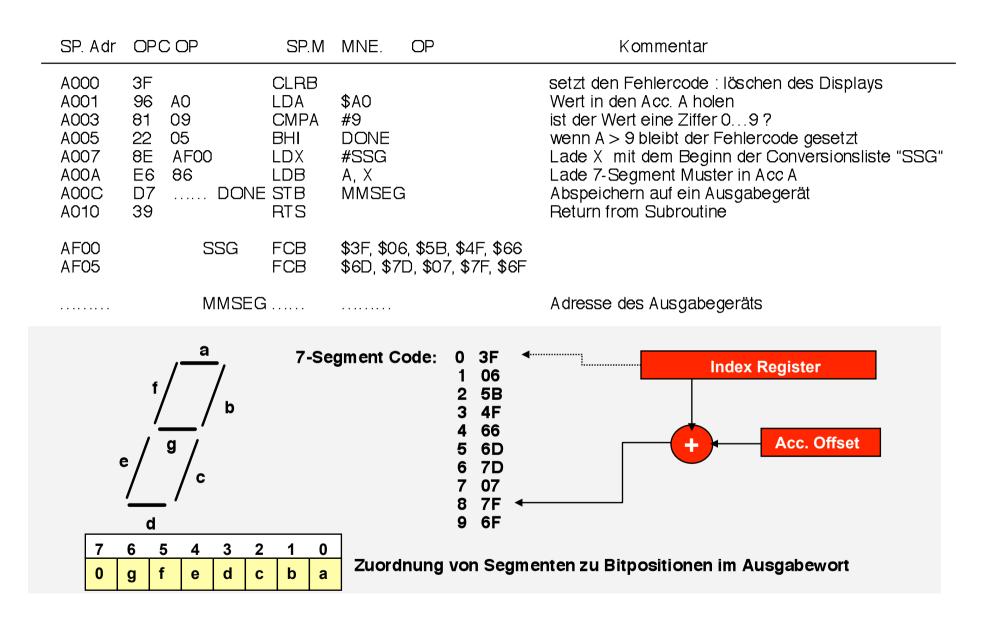

### Indizierte Adressierung beim MC 6809:

- Zero offset

- 5-Bit offset

- Long (16 Bit) constant offset

- Accumulator offset (Versatz kann verändert werden)

- Autoincrement

- Program Counter Relativ

- Relative Branches

- Indexed Indirect

# Grundformen der indizierten Adressierung

| Basisadresse                        | Versatz                                          | Bezeichnung                                                                                |

|-------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|

| (Index-) Register<br>X, Y, U, S, PC | Literal (kurz 5 Bit)<br>Speicher (lang 8/16 Bit) | Adressierung mit konstanter Distanzadresse<br>vom Indexregister<br>"Constant Offset Mode " |

| (Index-) Register<br>X, Y, U, S     | Register A, B, D                                 | Adressierung mit Distanzadresse aus dem Accumulator A, B oder D "Accumulator Offset"       |

| (Index-) Register<br>X, Y, U, S     | fest ±1, ±2                                      | Autoincrement / Autodecrement<br><u>POST</u> increment / <u>PRE</u> decrement              |

# Grundform der indiziert indirekten Adressierung

### 6809 Indizierte Adressierung (Indexed Adressing)

#### Modi für indizierte Adressierung:

| Konstanter Versatz            | Langform (zusätzliches Byte)  | lange Form(16 Bit)                 |

|-------------------------------|-------------------------------|------------------------------------|

|                               | Kurzform (Spez. im Post Byte) | kurze Form (8 Bit)<br>Versatz = 0  |

|                               | Programmzähler Offset         | Versatz ist 5-Bit lang<br>8/16 Bit |

| Accumulator Offset            | A, B und D                    |                                    |

| Auto Increment Auto Decrement | um 1 oder 2<br>um 1 oder 2    |                                    |

|                               | um i oder 2                   |                                    |

| Extended Indirect             |                               |                                    |

#### **Assembler Notation:**

| Notation                | Bedeutung                                                                                                                                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ,R<br>offset ,R         | das Register "R" (X, Y, U, S, PC) ist als Indexregister spezifiziert offset wird zum Indexregister "R" addiert                                                                                                  |

| label ,PCR              | Programmzähler-relative Adressierung – den Versatz zwischen PC und Label wird in der Assemblierungsphase berechnet und als konstanter Versatz im Modus: "constant PC-Offset" eingesetzt                         |

| ,R+(+)<br>, -(-)R<br>[] | Autoincrement um 1 (bzw. 2) des Registers "R" (X, Y, U, S, PC) (Postincrement)<br>Autodecrement um 1 (bzw 2) des Registers "R" (X, Y, U, S, PC) (Predecrement)<br>indizierte Adresse ist eine indirekte Adresse |

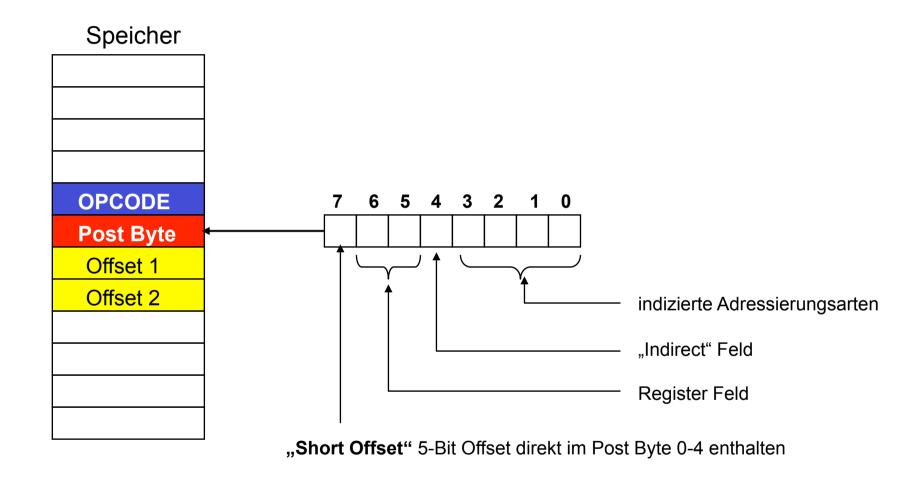

### Codierung der Indizierten Adressierungsarten

### **Belegung des Post Bytes**

| 7        | 6 |   |          | er |   |   |   | Addressing Mode    |  |  |  |

|----------|---|---|----------|----|---|---|---|--------------------|--|--|--|

| <u> </u> |   | 5 | 4        | 3  | 2 | 1 | 0 |                    |  |  |  |

|          | R | R | Χ        | Χ  | Χ | Χ | Χ | 5-Bit Offset       |  |  |  |

| 1        | R | R | 0        | 0  | 0 | 0 | 0 | Autoincrement by 1 |  |  |  |

| 1        | R | R | j        | 0  | 0 | 0 | 1 | Autoincrement by 2 |  |  |  |

| 1_       | R | R | 0        | 0  | 0 | 1 | 0 | Autodecrement by 1 |  |  |  |

| 1_       | R | R | i        | 0  | 0 | 1 | 1 | Autoincrement by 2 |  |  |  |

| 1        | R | R | i        | 0  | 1 | 0 | 0 | Zero Offset        |  |  |  |

| 1        | R | R | i        | 0  | 1 | 0 | 1 | Acc. B Offset      |  |  |  |

| 1_       | R | R | į        | 0  | 1 | 1 | 0 | Acc. A Offset      |  |  |  |

| 1_       | R | R | i        | 1  | 0 | 0 | 0 | 8-Bit Offset       |  |  |  |

| _1_      | R | R | <u>i</u> | 1  | 0 | 0 | 1 | 16-Bit Offset      |  |  |  |

| _1_      | R | R | i        | 1  | 0 | 1 | 1 | Acc. D Offset      |  |  |  |

| 1        | X | Х | i        | 1  | 1 | 0 | 0 | PC 8-Bit Offset    |  |  |  |

| 1        | X | Х | i        | 1  | 1 | 0 | 1 | PC 16-Bit Offset   |  |  |  |

| 1        | R | R | 1        | 1  | 1 | 1 | 1 | Extended Indirect  |  |  |  |

|          |   |   |          |    |   |   |   |                    |  |  |  |

Addressing Mode

Indirect Field:i=1 for indirecti=0 for directsign bit when bit 7 =0

┌ Register Field:

00 R = X

01 R = Y

10 R = U

11 R = S

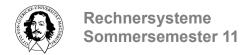

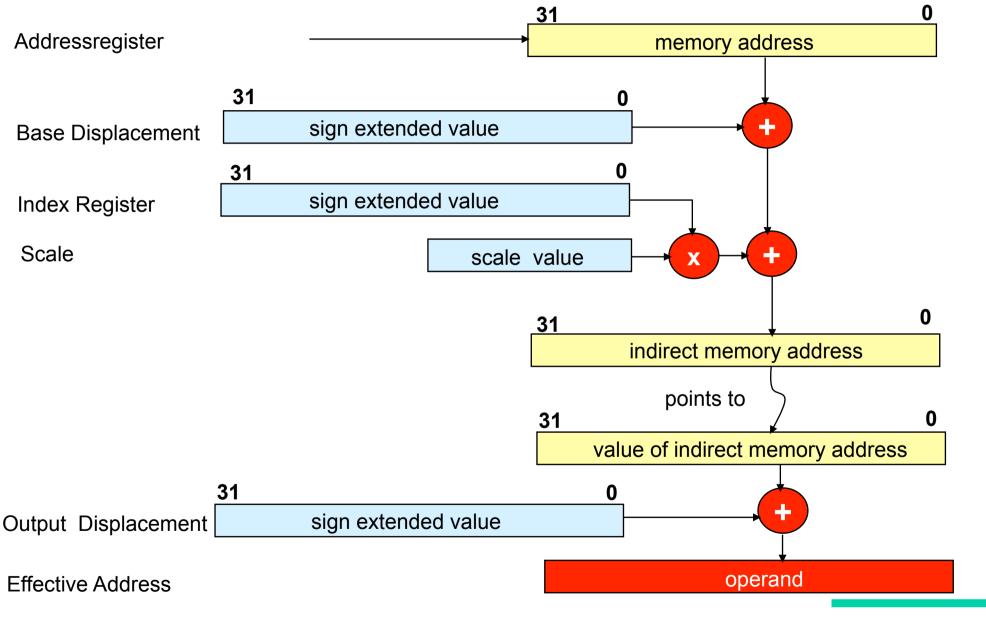

### Erweiterungen für die Indizierte Adressierung

#### **Basisform**

**Erweiterungen:**

- skalierter Index

- zusätzliche feste Distanzadressen

- Indirektion

#### Indiziert, indizierter, am ... Memory indirect pre-indexed Adressierungsart bei MC 68020

### **Architektur Varianten**

#### **Stack orientiert:**

Burroughs, Java VM

#### **Speicher orientiert:**

IBM 360 series, Accumulator-Architekturen, frühe Mikroprozessoren

#### **Register orientiert:**

DEC Alpha, ARM, Sparc, MIPS

#### **Hybrid:**

DEC VAX, Motorola 68K, IBM PowerPC, Intel x 86, Pentium II

### **Architektur Varianten**

### Instruktionen mit 0 Operanden (implizite Adressierung):

HIt, NOP, in Stack Architekturen auch Push, Pop und arithmetische und logische Befehle wie Add, Sub, Mult,...

#### Instruktionen mit 1 Operanden:

Not,Increment, Decrement, Jmp, Bra,... Bei Accumulatorarchitekturen auch alle zweistelligen arithm./log. Befehle

### Instruktionen mit 2 Operanden:

Datentransferbefehle wie Mov, Load, Store, zweistellige arithm./logische Operationen, ein Operand wird vom Resultat überschrieben.

### Instruktionen mit 3 Operanden:

zweistellige Operationen: Ziel← Qelle1 op Quelle2

#### Ein-Adreß-Befehl

Beisp.: Motorola 6809 OPCODE AdreBfeld

#### Zwei-Adreß-Befehl

Befehlsformate:

680x0, Intel 386,486 OPCODE AdreBfeld (Quelle) AdreBfeld (Ziel)

2.ter Quelloperand steht an Zieladresse und wird durch Operation überschrieben

Beisp.: Motorola 680x0 4 3 3 6

OPCODE REG MOD MOD Adreβfeld REG

Register Register #

Speicher kurz, lang

#### Drei-Adreß-Befehl

MIPS, Alpha, SPARC

| OPCODE Adreßfeld (Quelle 1) | AdreBfeld (Quelle 2) | Adreßfeld (Ziel) |

|-----------------------------|----------------------|------------------|

|-----------------------------|----------------------|------------------|

Beisp. MIPS

| 6      | 5  | 5  | . 5     | 5    | 6 |  |  |  |

|--------|----|----|---------|------|---|--|--|--|

| OPCODE | rs | rt | rd      | func |   |  |  |  |

| OPCODE | rs | rt | Adresse |      |   |  |  |  |

rs: erstes Quellreg. rt: zweites Quellreg.

rd: Zielreg.

shamt: shift amount func: funktionale Erw. des OPCODE

### Lernziele

- Aufbau eines realen einfachen Prozessors

- Befehlssatz

- Standardbefehle (arithm./log., Shift, Transfer, System)

- Sprünge und Unterprogrammaufruf

- Behandlung von Bedingungen

- Spezifikation von bedingten Verzweigungen

- Adressierungsarten

- Zielkonflikte bei der Adressierung

- gängige Adressierungarten

- einfache Programme in Assembler unter Ausnutzung der Befehls- und Adressierungsmöglichkeiten.